Homepage / FROM CHIPS TO SYSTEM / SILICON INTERPOSER ANALYSIS AND DESIGN

Systems on Chip Design

• Source synchronous architecture is used to enable multiple chiplets to be integrated into a single system-on-chip with low latency.

• To ensure low error rates, the clock strobe and data channels need to be precisely matched

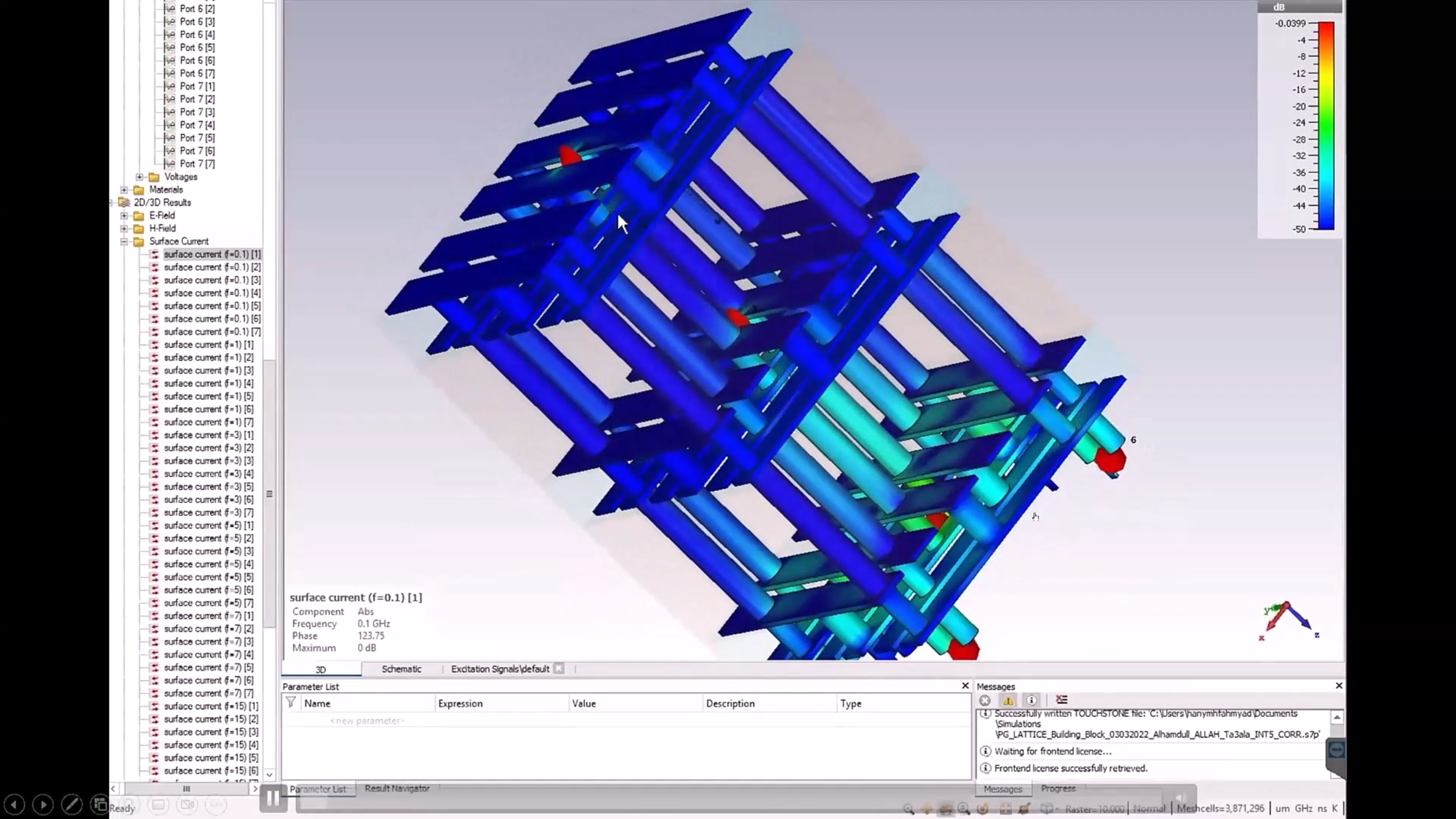

• See how to analyze and optimize source synchronous architecture with Electromagnetic Simulation